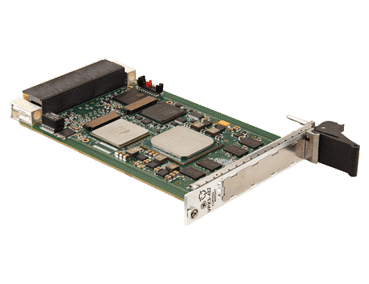

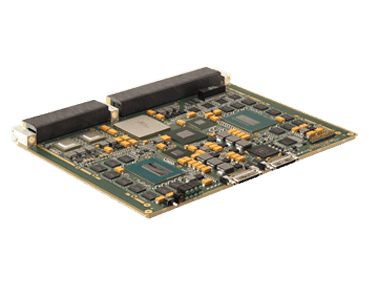

CHAMP-XD1S

For highly compute-intensive Industrial, Aerospace, and Defense applications where security is critical, the CHAMP-XD1S Digital Signal Processor (DSP) provides enhanced Trusted Computing features alongside leading-edge processing technology for unmatched performance.

Overview

The Curtiss-Wright 3U OpenVPX™ CHAMP-XD1S (VPX3-482S) security-enhanced, rugged Digital Signal Processor (DSP) engine module is designed for use in very compute-intensive Industrial, Aerospace & Defense applications.

This High Performance Embedded Computing (HPEC) module delivers incredible processing capability by pairing an 8 or 12-core Intel Xeon D processor with a Xilinx MPSoC Field Programmable Gate Array (FPGA). Its XMC mezzanine site allows system designers to add even more processing capability within a single slot.

Ideal for ISR applications, such as SIGINT, EW, and SAR, the CHAMP-XD1S delivers impressive capability in a 3U VPX board. The CHAMP-XD1S combines the high core count and floating-point performance of the latest Intel Xeon D processors with the substantial bandwidth and system-enabling features of the VITA 3U OpenVPX form-factor. As well, it includes a Xilinx ZU4EG FPGA with a quad-core A53 processor and an XMC mezzanine site to add additional processing capability.

The CHAMP-XD1S provides FPGA and software security features complemented by TrustedCOTS Enhanced Trusted Boot capabilities, including an FPGA-based Root of Security to protect against malicious cyber attacks, probing, and reverse-engineering.

The CHAMP-XD1S supports 1 Gigabit (Gb) or 10 Gigabit Ethernet (GbE) interfaces along the OpenVPX control plane, as well as PCI Express Gen3 on the data plane. Its XMC mezzanine site adds even more configuration flexibility, with a myriad of mezzanine cards available from both Curtiss-Wright and other industry vendors.

Choose from variants to support your specific requirements, including models developed in alignment with the SOSA Technical Standard or E-OSA specifications.

Specification

- Intel Xeon D 12-Core (576 @ 1.5 GHz)

- Extended operating temperature Intel eTEMP SKUs

- PCH integrated in Xeon D SoC

- Xilinx MPSoC FPGA with embedded quad A53 processor and 4 GB of DDR4 memory for enhanced security or coprocessor functionality

- Microchip SmartFusion2 FPGA for Tier2 IPMI with HOST 3.0 support

- Native dual KR 10 GigE ports

- 32 GB DDR4 @ 2133 mega-transfers per second (34 GB/s aggregate)

- XMC PCIe up to Gen3

- PCIe Gen3 on 3U OpenVPX data plane

- Conduction-cooled (L200)

- TrustedCOTS protections

- Variants aligned with the SOSA Technical Standard or E-OSA specifications available